(Autonomous) (ISO/IEC - 27001 - 2005 Certified)

## SUMMER – 2019 EXAMINATION MODEL ANSWER

#### **Subject: Digital Techniques and Microprocessor**

Subject Code:

22323

## **Important Instructions to examiners:**

- 1) The answers should be examined by key words and not as word-to-word as given in the model answer scheme.

- 2) The model answer and the answer written by candidate may vary but the examiner may try to assess the understanding level of the candidate.

- 3) The language errors such as grammatical, spelling errors should not be given more Importance (Not applicable for subject English and Communication Skills).

- 4) While assessing figures, examiner may give credit for principal components indicated in the figure. The figures drawn by candidate and model answer may vary. The examiner may give credit for any equivalent figure drawn.

- 5) Credits may be given step wise for numerical problems. In some cases, the assumed constant values may vary and there may be some difference in the candidate's answers and model answer.

- 6) In case of some questions credit may be given by judgement on part of examiner of relevant answer based on candidate's understanding.

- 7) For programming language papers, credit may be given to any other program based on equivalent concept.

| Q. | Sub  | Answer                                                                                                                                                                                                                                                                                            | Marking   |

|----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| No | Q.N. |                                                                                                                                                                                                                                                                                                   | Scheme    |

|    |      |                                                                                                                                                                                                                                                                                                   |           |

| 1. |      | Attempt any <b><u>FIVE</u> of the following:</b>                                                                                                                                                                                                                                                  | 10        |

|    | a)   | State the function of linker and debugger.                                                                                                                                                                                                                                                        | <b>2M</b> |

|    | Ans. | Function of linker and debugger:                                                                                                                                                                                                                                                                  |           |

|    |      | Linker: There are certain programs which are large in size and                                                                                                                                                                                                                                    |           |

|    |      | cannot be executed at one go simultaneously. Such programs are                                                                                                                                                                                                                                    |           |

|    |      | divided into sub programs also known as modules. The linker is used                                                                                                                                                                                                                               | Each      |

|    |      | to link such small programs to form one large program. It also                                                                                                                                                                                                                                    | function  |

|    |      | generates an executable file.                                                                                                                                                                                                                                                                     | <i>1M</i> |

|    |      | <b>Debugger:</b> Debugger is used to test and debug programs. The debugger allows a user to test a program step by step, so that the problem points or steps can be identified and rectified. It allows the user to inspect the registers and memory locations after a program has been executed. |           |

|    | b)   | List any four addressing modes and give one example of each.                                                                                                                                                                                                                                      | <b>2M</b> |

|    | Ans. | Addressing Modes:                                                                                                                                                                                                                                                                                 |           |

|    |      | 1. Immediate Addressing Mode:                                                                                                                                                                                                                                                                     |           |

|    |      | Example: MOV CL, 03H                                                                                                                                                                                                                                                                              |           |

|    |      | ADD AX, 1234H                                                                                                                                                                                                                                                                                     |           |

(Autonomous) (ISO/IEC - 27001 - 2005 Certified)

## SUMMER – 2019 EXAMINATION MODEL ANSWER

Subject: Digital Techniques and Microprocessor

Subject Code:

22323

| c)<br>Ans. | Example: IN AL, DX<br>OUT DX, AX11. Implied (Implicit) Addressing Modes<br>Example: CLC<br>DAAState any two Boolean laws with expression.1. $A . 0 = 0$<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2M<br>Any 2<br>Boolean<br>laws 1M<br>each                                             |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

|            | <ol> <li>Register Addressing Mode:<br/>Example: MOV AL, BL<br/>ADD CL, DL<br/>MOV DS, AX</li> <li>Direct Addressing Mode:<br/>Example: MOV AL, [2000H]<br/>MOV [1020], 5050H</li> <li>Register Indirect Addressing Mode<br/>Example: MOV [DI], 1234H<br/>MOV AX, [BX]</li> <li>Based Addressing with displacement<br/>Example: MOV AX, [BX+300H]<br/>MOV AX, [BX-2H]</li> <li>Indexed Addressing Mode<br/>Example: MOV [DI + 2345H], 1234H<br/>MOV AX, [SI + 45H]</li> <li>Based Indexed Addressing Mode<br/>Example: MOV [BX + DI], 1234H<br/>MOV AX, [SI + 45H]</li> <li>Based Indexed Addressing with Displacement Mode<br/>Example: MOV [DI + BX + 37H], AX<br/>MOV AL, [BX + SI + 278H]</li> <li>Fixed or Direct Port Addressing:<br/>Example: OUT 06H, AL<br/>IN AX, 85H</li> <li>Variable or Indirect Port Addressing</li> </ol> | Any<br>four<br>addressi<br>ng<br>modes<br>with<br>example<br><sup>1/2</sup> M<br>each |

(Autonomous) (ISO/IEC - 27001 - 2005 Certified)

## SUMMER – 2019 EXAMINATION MODEL ANSWER

Subject: Digital Techniques and Microprocessor

| d)<br>Ans. | A.(B+C) = A.B + A.C.<br>8. A.(A+B) = A<br>9. A. $(\overline{A} + B) = AB$<br>10. $\overline{A} = A$<br>11. De-Morgan's theorem<br>$\overline{A \cdot B} = \overline{A} + \overline{B}$<br>12. $A + 0 = A$<br>13. $A + 1 = 1$ $\overline{A} + 1 = 1$<br>14. $A + A = A$<br>15. $A + \overline{A} = 1$<br>16. $A + B = B + A$<br>17. $A + (B + C) = (A + B) + C$<br>18. $A + (B. C) = (A + B) \cdot (A + C)$<br>19. $A + AB = A$<br>20. $A + \overline{AB} = A + B$<br>21. $\overline{A} + AB = \overline{A} + \overline{B}$<br>22. $\overline{A} + A\overline{B} = \overline{A} + \overline{B}$<br>23. $\overline{A + B} = \overline{A} + \overline{B}$<br>19. <b>Define:</b><br>1) <b>Bit</b><br>10. <b>Bit</b> : Bit is a Binary digit which is the smallest unit of data in | 2M<br>Each        |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

|            | <ul><li>digital systems. A bit has a single binary value, either 0 or 1.</li><li>ii) Nibble: A group of 4 bits is referred as Nibble. Eg: 1011, 1001, 1100</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | definitio<br>n 1M |

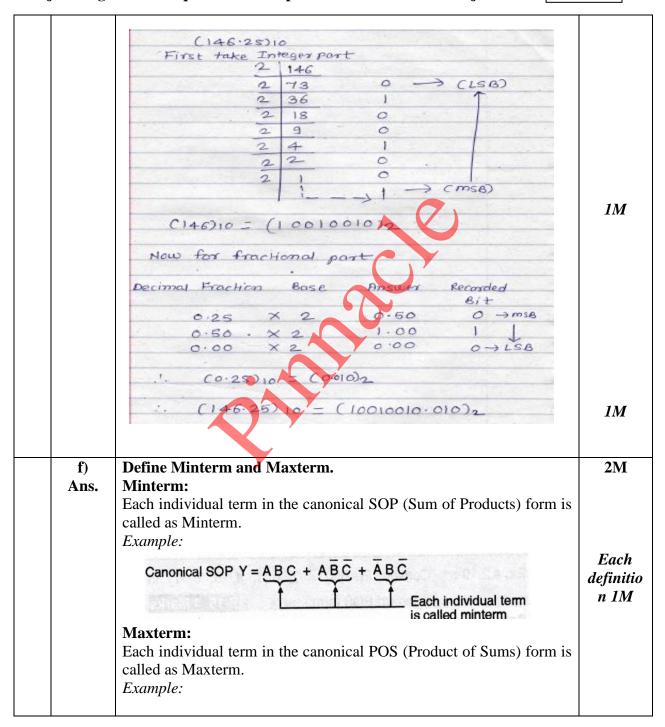

| e)<br>Ans. | Convert following number into its equivalent Binary Number (146.25) <sub>10</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2M                |

MAHARASHTRA STATE BOARD OF TECHNICAL EDUCATION (Autonomous)

(ISO/IEC - 27001 - 2005 Certified)

## SUMMER – 2019 EXAMINATION MODEL ANSWER

Subject: Digital Techniques and Microprocessor

Subject Code:

22323

(Autonomous) (ISO/IEC - 27001 - 2005 Certified)

## SUMMER – 2019 EXAMINATION MODEL ANSWER

Subject: Digital Techniques and Microprocessor Subject Code:

. 22323

Page 5 / 27

22323

Subject Code:

**Subject: Digital Techniques and Microprocessor**

MAHARASHTRA STATE BOARD OF TECHNICAL EDUCATION

(Autonomous) (ISO/IEC - 27001 - 2005 Certified)

## SUMMER – 2019 EXAMINATION MODEL ANSWER

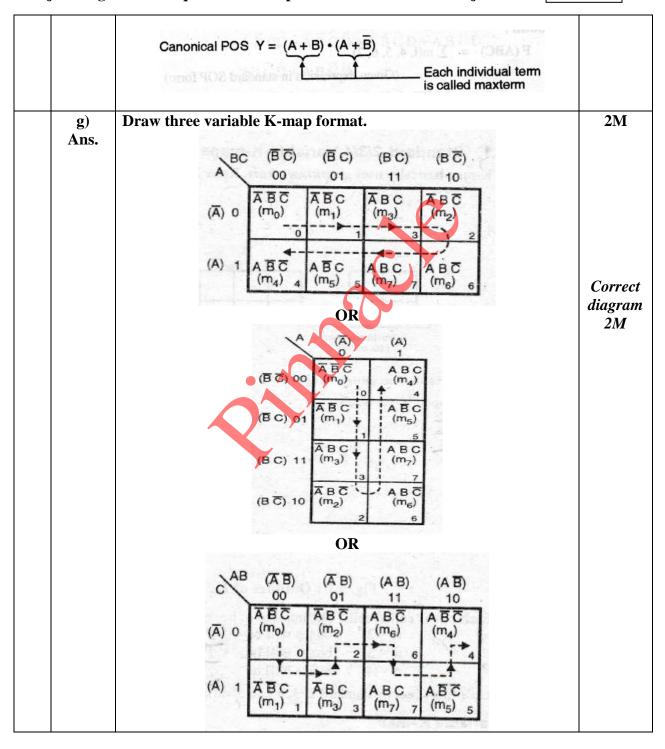

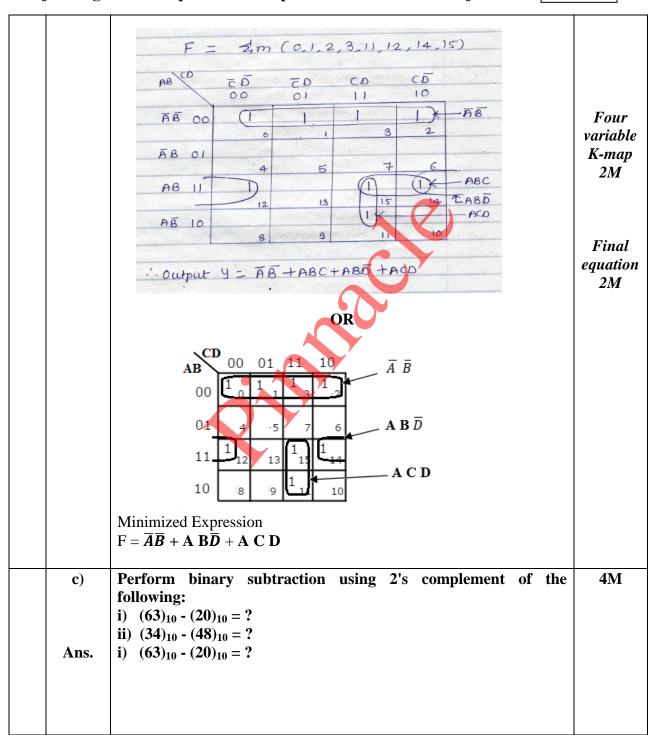

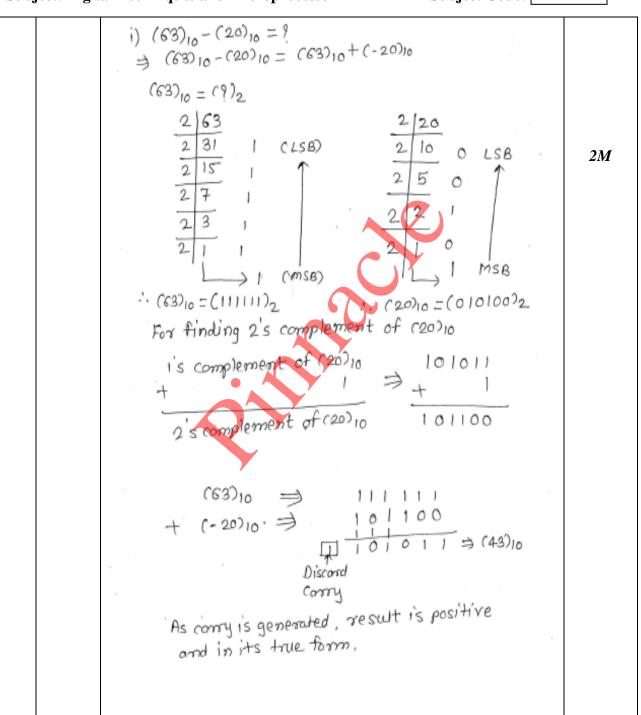

2 Attempt any <u>THREE</u> of the following: 12 Draw symbol and truth table of D and T flip flop. State theie **4M** a) applications. D flip flop: Ans. Output Input Q. + 1 D Q. + 1 CLK I/Po NC NC 0 x D flip x NC NC 1 flop CLK DFF x NC NC Symbol -1  $1/_{2}M;$ 1 0 . 1 Truth 1 0 table-Symbol **Truth Table** *1M*; **Applications of D flip flop:** One 1. used as a Latch applicati 2. Divide - by - 4 Ripple Counter on  $-\frac{1}{2}M$ 3. Ring Counter 4. Johnson Counter 5. Used in registers T flip flop:  $\overline{Q}_{n+1}$ T flip  $Q_{n+1}$ CLK Т flop CLK Q<sub>n</sub> Qn TFF 0 Symbol -Qn  $1/_{2}M;$ Qn Truth O table-*1M*; Symbol **Truth Table** One applicati **Applications of T flip flop:** on  $-\frac{1}{2}M$ 1. As the basic building block of counter. 2. In frequency divider circuits. 3. Used in D to A converter (DAC) Minimize the following function using K-map. b) **4M**  $\mathbf{F} = \Sigma \mathbf{m} (0,1,2,3,11,12,14,15).$ (Note: Any other equations shall be considered). Ans.

MAHARASHTRA STATE BOARD OF TECHNICAL EDUCATION (Autonomous)

(ISO/IEC - 27001 - 2005 Certified)

## SUMMER – 2019 EXAMINATION MODEL ANSWER

Subject: Digital Techniques and Microprocessor

MAHARASHTRA STATE BOARD OF TECHNICAL EDUCATION (Autonomous)

(ISO/IEC - 27001 - 2005 Certified)

## SUMMER – 2019 EXAMINATION MODEL ANSWER

**Subject: Digital Techniques and Microprocessor**

Subject Code: 22323

MAHARASHTRA STATE BOARD OF TECHNICAL EDUCATION (Autonomous)

(ISO/IEC - 27001 - 2005 Certified)

## SUMMER – 2019 EXAMINATION MODEL ANSWER

shall also be considered.

Ans.

SUPPORT OF TROPPORT

MAHARASHTRA STATE BOARD OF TECHNICAL EDUCATION

(Autonomous) (ISO/IEC - 27001 - 2005 Certified)

#### SUMMER – 2019 EXAMINATION MODEL ANSWER

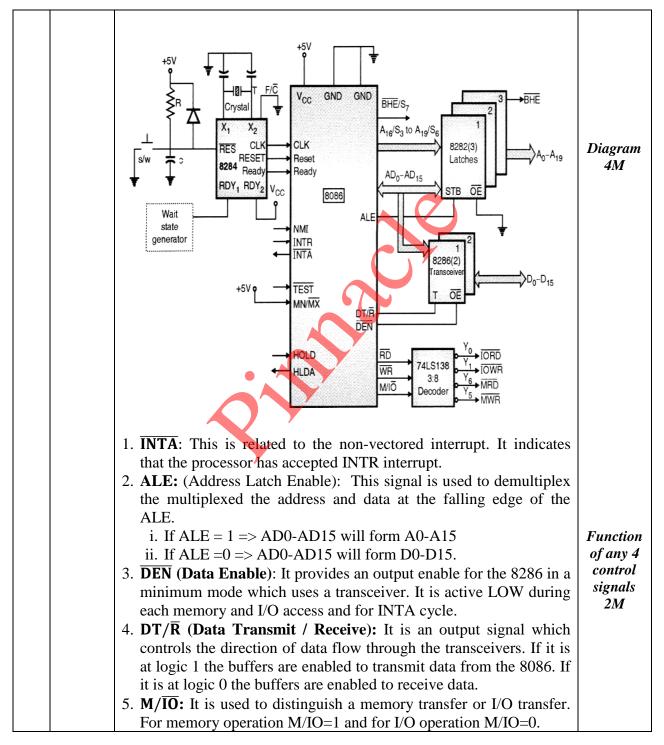

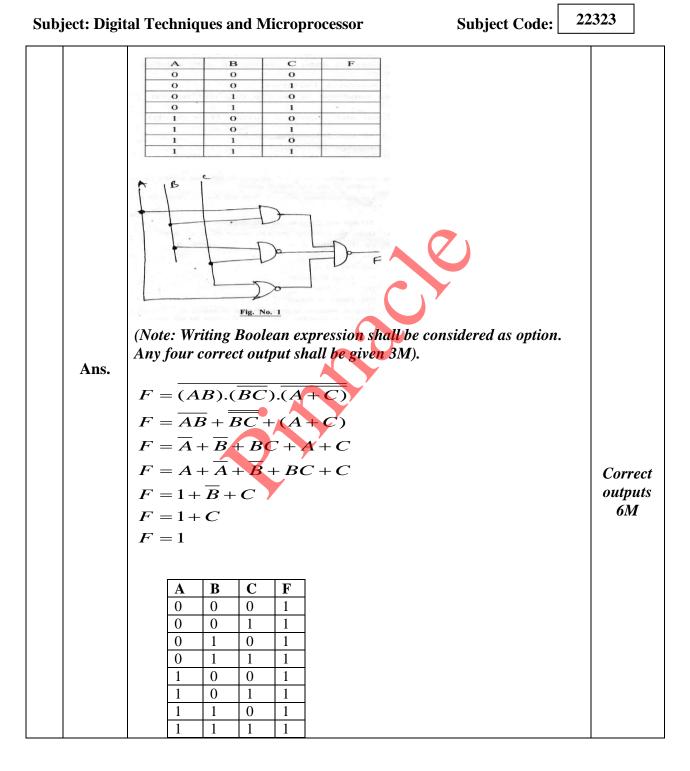

22323 Subject Code: **Subject: Digital Techniques and Microprocessor**  $\therefore 1 + C = C, B + \overline{B}C = B + C$  $= AB + \overline{A}(B + C)$  $= AB + \overline{A}B + \overline{A}C$  $= B (A + \overline{A}) + \overline{A}C$  $\therefore A + \overline{A} = 1$ 2M  $= B(1) + \overline{A}C$  $= \mathbf{B} + \overline{\mathbf{A}}\mathbf{C}$ ii)  $\mathbf{Y} = (\mathbf{A} + \mathbf{B}) (\mathbf{A} + \overline{\mathbf{B}}) (\overline{\mathbf{A}} + \mathbf{B})$  $= (A.A + A \overline{B} + AB + B \overline{B}) (\overline{A} + B)$  $= (A + A \overline{B} + AB + 0) (\overline{A} + B)$  (: A.A = A, B  $\overline{B}$  =0)  $= A (1 + \overline{B} + B) (\overline{A} + B)$ 2M  $= A(1)(\overline{A} + B)$  $(: B + \overline{B} = 1, 1 + A = 1)$  $= A (\overline{A} + B)$  $= A \overline{A} + AB$ = 0 + AB $(\because A \overline{A} = 0)$ = AB3. Attempt any <u>THREE</u> of the following: 12 Draw 8086 architecture block diagram and state the functions of **4M** a) EV and B/V. (Note: EV and B/V are considered as EU and BIU). Ans. MEMORY 810 INSTRUCTION STREAM BYTE QUEUE Diagram 2M CONTROL SYSTEM ΕIJ A-BUS ARITHMETIC CH OPERANDS FLAGS Fig: Functional Block Diagram of Intel 8086 microprocessor

Page 10 / 27

(Autonomous) (ISO/IEC - 27001 - 2005 Certified)

## SUMMER – 2019 EXAMINATION MODEL ANSWER

| Subject: Digi | tal Techniques and Microprocessor Subject Code: 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 323                            |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

|               | <ul> <li>BIU: It handles all transfers of data and addresses on the buses for the execution unit.</li> <li>Sends out addresses</li> <li>Fetches instructions from memory.</li> <li>Read / write data from/to ports and memory i.e. handles all transfers of data and addresses on the busses</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1M for<br>BIU                  |

|               | <ul> <li>EU: <ul> <li>Tells BIU where to fetch instructions or data from</li> <li>Decodes instructions</li> <li>Executes instructions</li> </ul> </li> <li>OR <ul> <li>The functions performed by the Bus interface unit are: <ul> <li>The BIU is responsible for the external bus operations.</li> <li>It performs fetching, reading, writing for memory as well as I/O of data for peripheral devices.</li> <li>The BIU also performs address generation and the population of the instruction queue.</li> </ul> </li> <li>The Execution unit is responsible for the following work: <ul> <li>The instructions are decoded and executed by it.</li> <li>The EU accepts instructions from the instruction queue and from the general purpose registers it takes data.</li> <li>It has no relation with the system buses.</li> </ul> </li> </ul></li></ul> | 1M for<br>EU                   |

| b)<br>Ans.    | <ul> <li>Design half adder using K-map and realize it using basic gate.</li> <li>Half Adder:</li> <li>Half adder is a combinational circuit that performs simple addition of two binary digits.</li> <li>Half Adder Truth Table:</li> <li>If we assume A and B as the two bits whose addition is to be performed, a truth table for half adder with A, B as inputs and Sum, Carry as outputs can be tabulated as follows.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                       | 4M<br>1M for<br>Truth<br>Table |

(Autonomous) (ISO/IEC - 27001 - 2005 Certified)

## SUMMER – 2019 EXAMINATION MODEL ANSWER

22323 Subject Code: **Subject: Digital Techniques and Microprocessor** Truth Table Input Output 1M each В A Sum Carry for K 0 0 0 0 map of 0 1 0 1 sum and 1 0 1 0 carry 0 1 1 1 K map for sum 0 B 0 1 Sum = AB + ABK map for Carry 0 0 0 1 1 Carry=A.B Logic Diagram for Half Adder: 1M for А Logic Diagram

Page 12 / 27

(Autonomous) (ISO/IEC - 27001 - 2005 Certified)

## SUMMER – 2019 EXAMINATION MODEL ANSWER

Page 13 / 27

٦

Г

MAHARASHTRA STATE BOARD OF TECHNICAL EDUCATION

(Autonomous) (ISO/IEC - 27001 - 2005 Certified)

## SUMMER – 2019 EXAMINATION MODEL ANSWER

Page 14 / 27

(Autonomous) (ISO/IEC - 27001 - 2005 Certified)

## SUMMER – 2019 EXAMINATION MODEL ANSWER

Page 15 / 27

A DECEMBER OF THE OWNER OWNER OF THE OWNER OWNE

MAHARASHTRA STATE BOARD OF TECHNICAL EDUCATION

(Autonomous) (ISO/IEC - 27001 - 2005 Certified)

## SUMMER – 2019 EXAMINATION MODEL ANSWER

Page 16 / 27

(Autonomous) (ISO/IEC - 27001 - 2005 Certified)

## SUMMER – 2019 EXAMINATION MODEL ANSWER

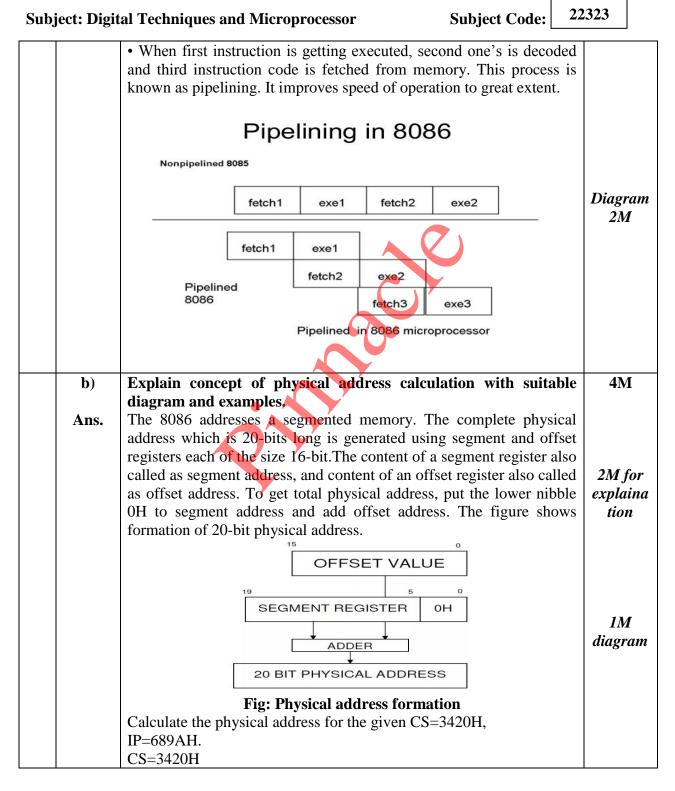

|            | IP=689A      Zero is in      3 4 2 0      + 6 8 9      = 3 A A 9 | serted<br>) 0<br>) A    |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            | 1M fo<br>examp |

|------------|------------------------------------------------------------------|-------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------|

| c)<br>Ans. | TheoremIt states tcompleme                                       | hat the,<br>ents        | -         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | o product of th            | 4M<br>neir     |

|            |                                                                  | A                       | B Ā       | + B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ĀB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Ā·Ē                        | For            |

|            |                                                                  | 0                       | 0         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1                          | each           |

|            |                                                                  | 0                       | 1         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0                          | theore         |

|            |                                                                  | 1                       | 0         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0 '                        | 2M             |

|            | Theorem                                                          | no 2:                   |           | LHS<br>le to verify                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | $\overline{\mathbf{A} + \mathbf{B}} = \overline{\mathbf{A}} \cdot$<br>De-Morgan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | B RHS<br>'s second theorem |                |

|            | <b>Theorem</b><br>It states to<br>compleme                       | that, the               | Truth tab | le to verify                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | De-Morgan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                            | the            |

|            | It states t                                                      | that, the               | Truth tab | le to verify                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | De-Morgan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 's second theorem          | the            |

|            | It states to<br>compleme                                         | that, the<br>ents.      | Compleme  | ent of a pr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>De-Morgan</b><br>oduct is eq                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 's second theorem          | the            |

|            | It states to<br>compleme                                         | that, the<br>ents.<br>B | Compleme  | ent of a pr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | De-Morgan<br>oduct is eq<br>B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 's second theorem          | the            |

|            | It states to complement                                          | that, the ents.         | Truck tab | ent of a pr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | De-Morgan<br>oduct is equivalent of the second | 's second theorem          | the            |

|            | It states to complement                                          | B<br>0<br>1             | Truck tab | ent of a provide the second se | De-Morgan<br>oduct is equivalent of the second | 's second theorem          | the            |

(Autonomous) (ISO/IEC - 27001 - 2005 Certified)

#### SUMMER – 2019 EXAMINATION MODEL ANSWER

| Subj | ject: Digit | tal Tech                                                                                                             | niques and Microprocesso                                                                                                                                                                                                                                                                                          | or Subject Code: 22                                                                                                                                                                                                                                                                                                                                                              | 2323                      |

|------|-------------|----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

|      | <b>d</b> )  |                                                                                                                      | be race-around condition<br>come it.                                                                                                                                                                                                                                                                              | in JK flip flop and suggest ways                                                                                                                                                                                                                                                                                                                                                 | <b>4M</b>                 |